Japan Industrial Imaging Association Guideline 日本インダストリアルイメージング協会 ガイドライン

JIIA CXPR-008-2023

# CoaXPress over Fiber Bridge Protocol

Version 1.1 Enacted on 2023.11.17 2023 年 11 月 17 日 制定

The Standardization Committee—CoaXPress Working Group

Japan Industrial Imaging Association

標準化委員会 CoaXPress 分科会 一般社団法人 日本インダストリアルイメージング協会

This document is provided "as it is" with this current version.

None of JIIA, its members including contributions to the standard are also made by members of the G3 Group of Associations, the subsidiary companies of its members or the affiliates of its members are liable, whether express or implied, for any kinds of warranties of merchantability, fitness for a particular purpose, and non-infringement of third party property rights.

JIIA, its members including Contributions to the standard are also made by members of the G3 Group of Associations, the subsidiary companies of its members, or the affiliates of its members are exempted from taking responsibility and held harmless under the applicable law, whether express or implied, for any kinds of damages or losses arising from a course of usage of this document, including but not limited to passive damages, derivative damages, and incidental damages. This is applied even when any of JIIA, its members including Contributions to the standard are also made by members of the G3 Group of Associations, the subsidiary companies of its members or the affiliates of its members were informed of the possibilities of damages in advance.

JIIA, its members including Contributions to the standard are also made by members of the G3 Group of Associations, the subsidiary companies of its members or the affiliates of its members are exempted from taking responsibility and held harmless for any litigation, including but not limited to on defending, on cooperating, and on compensating, and infringement of intellectual property rights with the third party, incurred by the usage of this document.

CoaXPress is a registered trademark in Japan, the USA, the EU, and other countries and the property of the trademark belongs to Japan Industrial Imaging Association (JIIA). You need a trademark license to use the logo on any product or in commercial documents. If you want to use the trademark or have any questions about using trademarks, please contact a JIIA representative (sec@jiia.org).

#### ©2023 Japan Industrial Imaging Association

この書面は"現状のまま"の状態で提供されます。

JIIA, またはG3加盟協会会員による規格化協力会員, 会員の子会社もしくは会員の関係会社のいずれも, この書面の内容に関して, 商品性, 特定の目的への適合性, 非侵害の保証を含め, いかなる保証も, 明示たると黙示たるとを問わず一切行いません。 JIIA, またはG3加盟協会会員による規格化協力会員, 会員の子会社もしくは会員の関連会社のいずれも, この書面の使用, また は使用不能から生ずるいかなる損害(逸失利益, 及びその他の派生的, または付随的な損害を含むが, これらに限定されない全 ての損害を言います。)について, 適用法で認められる限り, 一切の責任を負わないものとします。

たとえJIIA, またはG3加盟協会会員による規格化協力会員, 会員の子会社もしくは会員の関連会社がかかわる損害の可能性について知らされていた場合でも同様です。

JIIA, またはG3加盟協会会員による規格化協力会員, 会員の子会社もしくは会員の関連会社のいずれも, この書面に起因して第 三者との間に生じた, または生じうる知的財産権に関する紛争について, 防御, 協力, または補償する責任を負わないものとしま す。

CoaXPressは日本、アメリカ、EUその他の国に登録された商標であり、この商標権は一般社団法人日本インダストリアルイメージン グ協会に帰属します。製品または広報広告文書に使用する場合には使用許諾が必要となります。商標の使用を望まれる場合もし くは使用に関し疑義がある場合にはJIIA担当(sec@jija.org)まで連絡をお願いします。

#### ©2023 一般社団法人 日本インダストリアルイメージング協会

# TABLE OF CONTENTS

| 1     | Scope                                      | 5  |

|-------|--------------------------------------------|----|

| 2     | References and Definitions of Terms        | 5  |

| 2.1   | Normative References                       | 5  |

| 2.2   | Definitions of Terms                       | 5  |

| 2.3   | Abbreviations                              | 5  |

| 2.4   | Conventions                                | 6  |

| 3     | Introduction                               | 7  |

| 4     | Ethernet – IEEE Std 802.3                  | 9  |

| 4.1   | 10G and 25G Media Independent Interfaces 1 | 0  |

| 4.2   | Forward Error Correction1                  | 1  |

| 4.2.1 | IEEE802.3 Clause 74 1                      | 1  |

| 4.2.2 | IEEE802.3 Clause 1081                      | 2  |

| 5     | CoaXPress - Link structure and protocol1   | 3  |

| 5.1   | Link overview1                             | 3  |

| 5.2   | Data organization1                         | 4  |

| 5.3   | Packet transmission priority1              | 4  |

| 5.4   | Idle transmission1                         | 4  |

| 5.5   | Packet format1                             | 5  |

| 5.5.1 | Low-speed connection trigger1              | 5  |

| 5.5.2 | High-speed connection trigger1             | 5  |

| 5.5.3 | I/O acknowledgment1                        | 6  |

| 5.5.4 | Data packet transmission1                  | 6  |

| 5.6   | Support of 25G fiber bit rate1             | 6  |

| 6     | CXP-PHY bridge specification1              | 8  |

| 6.1   | CoF physical layer topology1               | 8  |

| 6.2   | Bridge structure 1                         | 8  |

| 6.2.1 | CXP-PHY Bridge - Host 1                    | 9  |

| 6.2.2 | CXP-PHY Bridge – Device                    | 21 |

| 6.3   | Packet structure2                          | 22 |

| 6.3.1 | SOP – Start of Packet                      | 23 |

| 6.3.2 | EOP – End of Packet                        | 25 |

| 6.3.3 | IT – Idle Transfer                         | 26 |

| 6.3.4 | HDP – High-Speed Data Payload2             | 26 |

| 6.3.5 | HKP – High-Speed K-Code Payload2           | 26 |

| 6.3.6 | LSP – Low-Speed Payload2                   | 27 |

| 7                                                                                 | High-speed CXP-PHY mapping                                                                                                                                                                                                                                                                                                                                  | . 28                                                                                    |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 7.1                                                                               | CXP-to-PHY mapping                                                                                                                                                                                                                                                                                                                                          | . 28                                                                                    |

| 7.1.1                                                                             | CoaXPress 8B/10B IDLE words                                                                                                                                                                                                                                                                                                                                 | . 28                                                                                    |

| 7.1.2                                                                             | CoaXPress data packets                                                                                                                                                                                                                                                                                                                                      | . 28                                                                                    |

| 7.1.3                                                                             | High-priority packets                                                                                                                                                                                                                                                                                                                                       | . 29                                                                                    |

| 7.1.4                                                                             | Use of HKP words                                                                                                                                                                                                                                                                                                                                            | . 31                                                                                    |

| 7.2                                                                               | PHY-to-CXP mapping                                                                                                                                                                                                                                                                                                                                          | . 32                                                                                    |

| 7.3                                                                               | Overhead analysis                                                                                                                                                                                                                                                                                                                                           | . 32                                                                                    |

| 7.3.1                                                                             | Example 1 – Area Scan                                                                                                                                                                                                                                                                                                                                       | . 33                                                                                    |

| 7.3.2                                                                             | Example 2 – Line Scan                                                                                                                                                                                                                                                                                                                                       | . 34                                                                                    |

| 8                                                                                 | Low-speed CXP-PHY mapping                                                                                                                                                                                                                                                                                                                                   | . 35                                                                                    |

| 9                                                                                 | Discovery considerations                                                                                                                                                                                                                                                                                                                                    | . 37                                                                                    |

| 9.1                                                                               | Connection state                                                                                                                                                                                                                                                                                                                                            | . 37                                                                                    |

| 9.2                                                                               | Match Device transmitter and Host receiver bit rates                                                                                                                                                                                                                                                                                                        | . 38                                                                                    |

| 9.3                                                                               | Detection of high-speed upconnection                                                                                                                                                                                                                                                                                                                        | . 38                                                                                    |

| 9.3.1                                                                             | Setting the bit rate via the high-speed upconnection                                                                                                                                                                                                                                                                                                        | . 39                                                                                    |

|                                                                                   |                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| Annex                                                                             | A: Examples of CXP-to-PHY mapping                                                                                                                                                                                                                                                                                                                           | . 41                                                                                    |

| Annex Annex                                                                       | A: Examples of CXP-to-PHY mapping<br>Mapping isolated CXP packets                                                                                                                                                                                                                                                                                           |                                                                                         |

|                                                                                   |                                                                                                                                                                                                                                                                                                                                                             | . 41                                                                                    |

| A.1                                                                               | Mapping isolated CXP packets                                                                                                                                                                                                                                                                                                                                | . 41<br>. 42                                                                            |

| A.1<br>A.2                                                                        | Mapping isolated CXP packets                                                                                                                                                                                                                                                                                                                                | . 41<br>. 42<br>. 43                                                                    |

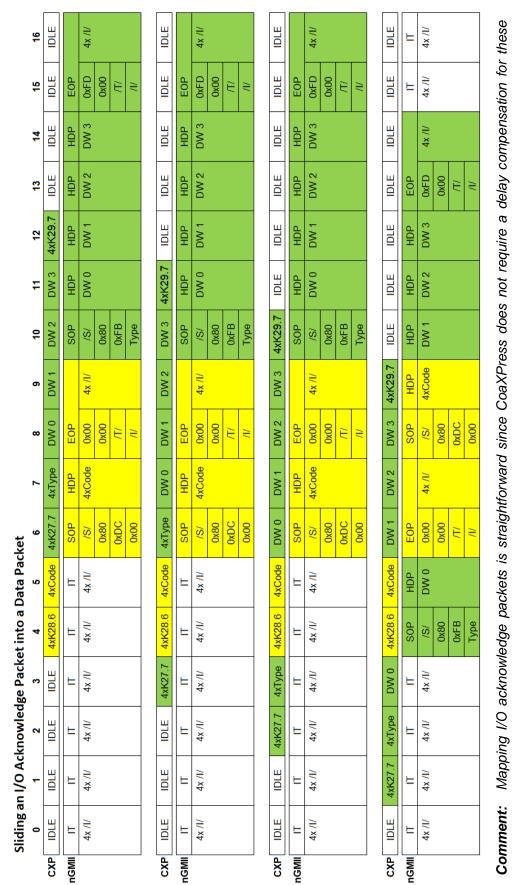

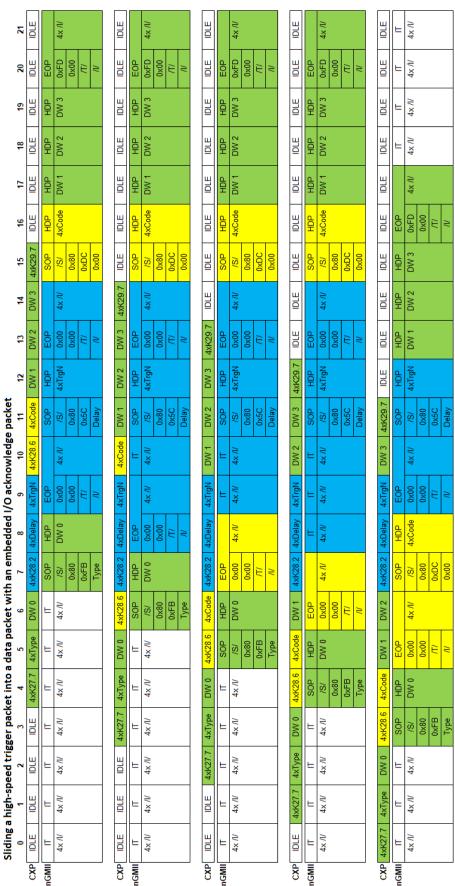

| A.1<br>A.2<br>A.3<br>A.4                                                          | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets                                                                                                                                                                                                                                                       | . 41<br>. 42<br>. 43<br>. 44                                                            |

| A.1<br>A.2<br>A.3<br>A.4                                                          | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets                                                                                                                                                                                                                      | . 41<br>. 42<br>. 43<br>. 44<br>. 45                                                    |

| A.1<br>A.2<br>A.3<br>A.4<br>Annex                                                 | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update                                                                                                                                                                                     | . 41<br>. 42<br>. 43<br>. 44<br>. 45<br>. 45                                            |

| A.1<br>A.2<br>A.3<br>A.4<br>Annex<br>B.1<br>B.1.1                                 | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update<br>Detection of High Speed Upconnection                                                                                                                                             | . 41<br>. 42<br>. 43<br>. 44<br>. 45<br>. 45<br>. 45                                    |

| A.1<br>A.2<br>A.3<br>A.4<br>Annex<br>B.1<br>B.1.1                                 | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update<br>Detection of High Speed Upconnection<br>JIIA CXP-001 - Section 12.1.5                                                                                                            | . 41<br>. 42<br>. 43<br>. 44<br>. 45<br>. 45<br>. 45<br>. 45                            |

| A.1<br>A.2<br>A.3<br>A.4<br>Annex<br>B.1<br>B.1.1<br>Annex                        | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update<br>Detection of High Speed Upconnection<br>JIIA CXP-001 - Section 12.1.5<br>C : Descriptive Clause                                                                                  | . 41<br>. 42<br>. 43<br>. 44<br>. 45<br>. 45<br>. 45<br>. 45<br>. 46                    |

| A.1<br>A.2<br>A.3<br>A.4<br>B.1<br>B.1.1<br>Annex<br>C.1                          | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update<br>Detection of High Speed Upconnection<br>JIIA CXP-001 - Section 12.1.5<br>C : Descriptive Clause<br>Background of CoaXPress over Fiber                                            | . 41<br>. 42<br>. 43<br>. 44<br>. 45<br>. 45<br>. 45<br>. 45<br>. 46<br>. 46            |

| A.1<br>A.2<br>A.3<br>A.4<br>B.1<br>B.1.1<br>Annex<br>C.1<br>C.2                   | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update<br>Detection of High Speed Upconnection<br>JIIA CXP-001 - Section 12.1.5<br>C : Descriptive Clause<br>Background of CoaXPress over Fiber.<br>Version History                        | . 41<br>. 42<br>. 43<br>. 44<br>. 45<br>. 45<br>. 45<br>. 46<br>. 46<br>. 46            |

| A.1<br>A.2<br>A.3<br>A.4<br>Annex<br>B.1<br>B.1.1<br>Annex<br>C.1<br>C.2<br>C.2.1 | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update<br>Detection of High Speed Upconnection<br>JIIA CXP-001 - Section 12.1.5<br>C : Descriptive Clause<br>Background of CoaXPress over Fiber<br>Version History                         | .41<br>.42<br>.43<br>.44<br>.45<br>.45<br>.45<br>.45<br>.46<br>.46<br>.46<br>.46        |

| A.1<br>A.2<br>A.3<br>A.4<br>B.1<br>B.1.1<br>Annex<br>C.1<br>C.2<br>C.2.1<br>C.2.2 | Mapping isolated CXP packets<br>Mapping I/O acknowledge packets<br>Mapping high-speed trigger packets<br>Mapping high-priority packets<br>B : CoaXPress Standard Update<br>Detection of High Speed Upconnection<br>JIIA CXP-001 - Section 12.1.5<br>C : Descriptive Clause<br>Background of CoaXPress over Fiber<br>Version History<br>v1.0<br>V1.0 to v1.1 | .41<br>.42<br>.43<br>.45<br>.45<br>.45<br>.45<br>.46<br>.46<br>.46<br>.46<br>.46<br>.46 |

# 1 Scope

The CoaXPress over Fiber Bridge Protocol was developed to allow employing optical fiber cables as transmission medium for the CoaXPress protocol. This document is intended to be used as a supplement to the existing CoaXPress standard.

# 2 References and Definitions of Terms

# 2.1 Normative References

The following referenced documents are essential for the application of this document. The latest edition of the referenced document (including any amendments) applies.

- Ref 1 IEEE 802.3: IEEE Standard for Ethernet

- Ref 2 JIIA CXP-001: CoaXPress Standard

- Ref 3 JIIA CXPR-007: Optical interface Guideline for CoaXPress

# 2.2 Definitions of Terms

8B/10B IDLE Refers to the CoaXPress 8B/10B encoded idle word formed by the characters K28.5, K28.1, K28.1, and D21.5.

nGMII Refers to both XGMII and 25GMII (see section 4.1).

nGMII IDLE Refers to XGMII and 25GMII idle control characters.

# 2.3 Abbreviations

| 25GMII | 25 Gigabit Media Independent Interface              |

|--------|-----------------------------------------------------|

| CoF    | CoaXPress over Fiber                                |

| CXP    | CoaXPress                                           |

| DW     | Data Word, 4 bytes                                  |

| EOP    | End of Packet                                       |

| FEC    | Forward Error Correction                            |

| Gbps   | Gigabit per second, 10 <sup>9</sup> bits per second |

| HDP    | High-Speed Data Payload                             |

| HKP    | High-Speed K-Code Payload                           |

| IPG    | Interpacket Gap                                     |

| IT     | Idle Transfer                                       |

| LSP    | Low-Speed Payload                                   |

| MAC    | Media Access Control                                |

| Mbps   | Megabit per second, 10 <sup>6</sup> bits per second |

| MDI    | Medium Dependent Interface                          |

| PCle   | Peripheral Component Interconnect Express |

|--------|-------------------------------------------|

| PCS    | Physical Coding Sublayer                  |

| PHY    | Ethernet Physical Layer                   |

| PMA    | Physical Medium Attachment                |

| PMD    | Physical Medium Dependent                 |

| RS-FEC | Reed-Solomon Forward Error Correction     |

| RXC    | Receive Control                           |

| RXD    | Receive Data                              |

| SerDes | Serializer/Deserializer                   |

| SOP    | Start of Packet                           |

| TXC    | Transmit Control                          |

| TXD    | Transmit Data                             |

| XGMII  | 10 Gigabit Media Independent Interface    |

# 2.4 Conventions

"Shall" means a mandatory requirement.

"Can" means an optional feature.

Comments written in italic text do not form part of the specification but are intended to help understand the requirements of the specification.

# 3 Introduction

CoaXPress is a successful interface protocol that is being largely used in the machine vision industry to connect high-end cameras to PCIe frame-grabbers. The main features that make CoaXPress appealing for this sector are its high bandwidth, highly deterministic triggers, long cable lengths, simplicity and robustness of cables and connectivity.

To meet the continuously increasing requirements of the machine vision industry, CoaXPress must cope with even higher bandwidths and longer cable lengths. Meeting these requirements using coaxial cables is unlikely to be feasible. Optical fiber cables are the most viable existing transmission medium that supports these requirements.

Optical fiber cables are massively used in Ethernet applications. Cables and peripheral components supporting very high bandwidths and extreme long distances have become accessible in terms of price and availability.

FPGAs already in use in CoaXPress applications include many features to support the Ethernet standard. This creates a natural path to employ optical fiber cables as transmission medium for the CoaXPress protocol.

The 10 Gigabit Media Independent Interface (XGMII), defined by IEEE Std 802.3 Clause 46, is the main access to the 10G Ethernet physical layer. The generic nature of this interface facilitates mapping the CoaXPress signaling into the PCS/PMA Ethernet sublayers. In addition, an XGMII interface has an effective bit rate equivalent to a CoaXPress CXP-12 connection without its 8B/10B encoding overhead. Slower CoaXPress bit rates can also be mapped into an XGMII interface by extending the spacing between two packets, known as the interpacket gap (IPG).

The use of the XGMII also allows CoaXPress to be ready to support higher bandwidths via the 25 Gigabit Media Independent Interface (25GMII), defined by IEEE Std 802.3 Clause 106. The 25GMII is a speededup version of the XGMII while being logically equivalent to it.

This document defines the CoaXPress over Fiber concept based on a physical layer topology and on a series of rules to map the CoaXPress protocol to the interface of the Ethernet physical layer. Based on these rules, a CoaXPress to Ethernet Physical Layer bridge (CXP-PHY bridge) is specified to allow the CoaXPress protocol to be transported over available Ethernet components without the need to establish new fiber components for the CoaXPress standard. The CXP-PHY bridge specification targets the following requirements:

- The CXP-PHY bridge must be transparent to the adjacent CoaXPress layer (Host or Device).

- The CXP-PHY bridge must (as much as possible) be independent from CoaXPress version variations (current and future ones).

- The CXP-PHY bridge must not perform any CoaXPress protocol decoding during mapping. Only K-code detection and high-priority packets identification are required.

For additional information regarding fiber optical connectors and cables, please refer to the Optical Interface Guideline for CoaXPress (see section 2.1, Ref 3).

# 4 Ethernet – IEEE Std 802.3

The IEEE Standard for Ethernet (see section 2.1, Ref 1) addresses Layer 1 (Physical) and Layer 2 (Data Link) of the Open Systems Interconnection model (OSI model) specified on ITU-T X.200.

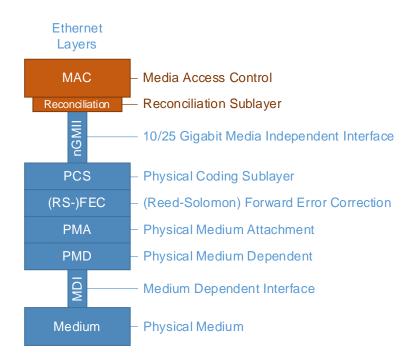

Figure 1 - Ethernet model for 10G and 25G BASE-R

To access the PCS/PMA sublayers, the CXP-PHY bridge replaces the Reconciliation Sublayer in the Ethernet model.

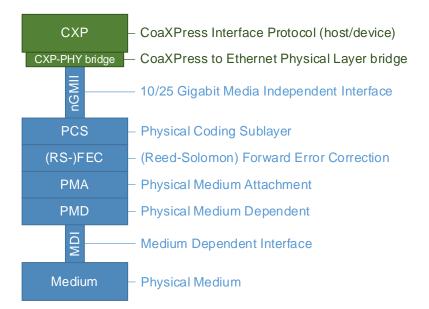

Figure 2 - Ethernet model in the CoaXPress over Fiber context

# 4.1 10G and 25G Media Independent Interfaces

The 10 Gigabit Media Independent Interface (XGMII) is defined by IEEE802.3 Clause 46 and provides an interconnection between the Media Access Control (MAC) and the 10G Ethernet Physical Layer (PHY).

The 25 Gigabit Media Independent Interface (25GMII) is a speeded-up version of the XGMII (2.5x faster) while being logically equivalent. It is defined by IEEE802.3 Clause 106 and provides an interconnection between the MAC and the 25G PHY.

XGMII TX/RX clock frequency is specified to be 156.25 MHz (+/- 0.01%) at DDR (Double Data Rate). In practice, the available FPGA PCS/PMA IPs work at SDR (Single Data Rate) at 312.5 MHz or with two aggregated interfaces at 156.25 MHz.

25GMII TX/RX clock frequency is specified to be 390.625 MHz (+/- 0.01%) at DDR. In practice, the available FPGA PCS/PMA IPs work at SDR with two aggregated interfaces at 390.625 MHz.

As both interfaces, XGMII and 25GMII, present the same encoding mechanism and identical structure of data and control paths, in this document they will be referenced as a single interface named *nGMII*.

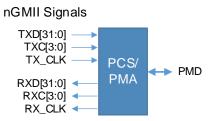

The nGMII is composed of two independent 32-bit data paths (TXD and RXD) each one associated to a 4bit control path (TXC and RXC). Each data path is organized into four 8-bit lanes.

Figure 3 - nGMII signals

A nGMII transfer contains four characters where each character is formed by 8 bits of data and 1 bit of control. In a nGMII transfer, the first character is aligned to lane 0, the second character is aligned to lane 1, and so on.

| TXD/RXD | TXC/RXC | Lane |

|---------|---------|------|

| [7:0]   | [0]     | 0    |

| [15:8]  | [1]     | 1    |

| [23:16] | [2]     | 2    |

| [31:24] | [3]     | 3    |

### Table 1 - nGMII data and control paths

The permissible lane encodings are:

| TXC/RXC | TXD/RXD           | Notation | Description                                                                                |

|---------|-------------------|----------|--------------------------------------------------------------------------------------------|

| 0       | 0x00 through 0xFF | /D/      | Normal data transfer                                                                       |

| 1       | 0x06              | /LI/     | Only valid on all four lanes<br>simultaneously to request/indicate Low<br>Power Idle (LPI) |

| 1       | 0x07              | /I/      | Idle (nGMII IDLE)                                                                          |

| 1       | 0x9C              | /Q/      | Sequence (only valid in lane 0)                                                            |

| 1       | 0xFB              | /S/      | Start (only valid in lane 0)                                                               |

| 1       | 0xFD              | /T/      | Terminate                                                                                  |

| 1       | 0xFE              | /E/      | Error                                                                                      |

| 1       | Others            | -        | Reserved                                                                                   |

Table 2 - nGMII permissible lane encodings

nGMII packets shall respect the following list of rules to be considered valid. These rules are based on the IEEE802.3 Clauses 46 (XGMII) and 106 (25GMII).

- nGMII Rule #1: /S/ is only valid at lane 0.

- nGMII Rule #2: /T/ is valid in any lane while the following lanes in the transfer must present /l/ characters.

- nGMII Rule #3: The minimum IPG at the nGMII is five characters.

- nGMII Rule #4: Between a /S/ and a /T/, only /D/ characters are considered valid.

- nGMII Rule #5: /LI/, /Q/, and /I/ characters are only allowed within the IPG.

# 4.2 Forward Error Correction

Forward Error Correction is a method to correct errors in a serial link by inserting additional information (check bits) in the transmitter data stream while the receiver decodes this information to verify the correctness of the data and to correct possible errors. This method improves the Bit Error Rate (BER) performance of a link without requiring a retransmission of the corrupted data.

The IEEE802.3 defines different types of FEC depending on the type of PHY implemented. For 10G and 25G BASE-R PHYs, the IEEE802.3 defines the respective FEC types in Clauses 74 and 108.

### 4.2.1 IEEE802.3 Clause 74

The IEEE802.3 Clause 74 defines the FEC sublayer for 10GBASE-R PHYs. The FEC Clause 74, also known as *Firecode FEC* or *BASE-R FEC*, can correct burst errors of up to 11 bits per block of 32 64B/66B blocks.

**Note:** In the context of the CoaXPress over Fiber, the implementation of IEEE802.3 Clause 74 is mandatory in 10G applications.

### 4.2.2 IEEE802.3 Clause 108

The IEEE802.3 Clause 108 defines the Reed-Solomon FEC (RS-FEC) sublayer for 25GBASE-R PHYs. The RS-FEC can correct up to 7 symbols per FEC block.

**Note:** In the context of the CoaXPress over Fiber, the implementation of IEEE802.3 Clause 108 is mandatory in 25G applications.

# 5 CoaXPress - Link structure and protocol

This section summarizes the aspects of the CoaXPress protocol that are essential to define the mapping mechanism between CoaXPress and Ethernet PHY.

- **Note:** It is not the intention of this section to reproduce all details of the CoaXPress standard. It is strongly recommended to refer to the latest review of the CoaXPress standard for details (see section 2.1, Ref 2).

- **Note:** All definitions, figures, and tables presented in this section are adapted excerpts from the CoaXPress 2.1 standard (JIIA CXP-001-2021) and may differ from other versions of the standard.

# 5.1 Link overview

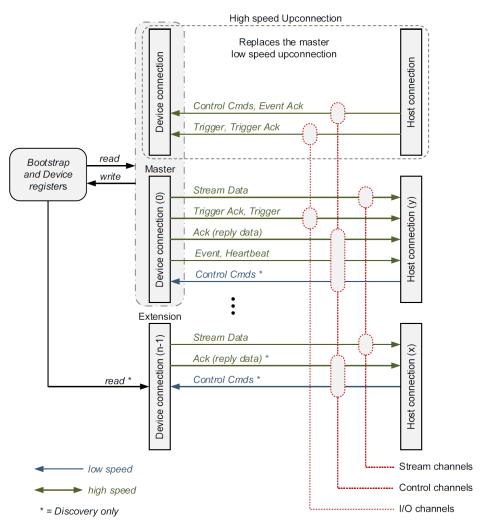

A CoaXPress link is defined as a point-to-point interface composed of one or more connections. Each connection consists of a high-speed downconnection (Device to Host) and a low-speed upconnection (Host to Device). Optionally, a high-speed upconnection can be used to increase the control channel bandwidth and the maximum trigger rate supported.

Figure 4 - CoaXPress link overview

Comment: The CoaXPress 2.0 standard (JIIA CXP-001-2019) does not support high-speed upconnection in contrast with other versions of the standard.

Comment: While for coaxial media the high-speed upconnection was costly to be implemented on both Hosts and Devices, for optical media it comes virtually with no cost since Ethernet-compliant components are typically symmetrical with up and downconnections working at the same bitrate.

# 5.2 Data organization

CoaXPress specifies two different data organizations: one for high-speed connections and one for lowspeed connections. For high-speed connections, data transmission is organized in groups of four characters called a word. Each word consists of four consecutive 8B/10B characters labeled P0, P1, P2 and P3. For low-speed connections, data transmission is organized in single 8B/10B characters.

# 5.3 Packet transmission priority

CoaXPress defines three levels of packet transmission priorities specifying that a higher-priority packet can be inserted into a lower-priority one. The transmission of the lower-priority packet must be halted while the higher-priority packet is introduced in the data stream. The transmission of the lower-priority packet is resumed as soon as the higher-priority packet transmission is finished.

| Priority Level | Packet type                             |

|----------------|-----------------------------------------|

| 0 (highest)    | Trigger                                 |

| 1              | I/O acknowledgment (for trigger packet) |

| 2 (lowest)     | All other packets                       |

Table 3 - CoaXPress packet transmission priority

# 5.4 Idle transmission

CoaXPress specifies an 8B/10B encoded idle word (8B/10B IDLE word) that must be sent in both highspeed and low-speed connections when the respective connection is idle.

Table 4 - CoaXPress 8B/10B IDLE word format

| Word | P0    | P1    | P2    | P3    |

|------|-------|-------|-------|-------|

| IDLE | K28.5 | K28.1 | K28.1 | D21.5 |

8B/10B IDLE words are also regularly inserted in the data stream to guarantee word alignment and equalizer reference for the coaxial cable transceiver. In high-speed connections, 8B/10B IDLE words are sent at least once every 100 words and they can be embedded into any CoaXPress packet, except in trigger packets and I/O acknowledgement packets. In low-speed connections, they are sent at least once every 10,000 words and can also be embedded into any CoaXPress packet, except in trigger packets and I/O acknowledgement packets.

CoaXPress also permits stretching packets (other than trigger or I/O acknowledgment) in high-speed connections by inserting 8B/10B IDLE words. In low-speed connections, stretching packets is not allowed.

# 5.5 Packet format

The CoaXPress protocol employs four different packet formats to exchange data between Host and Device. Each one of these packet formats uses one or more 8B/10B K-code characters to indicate, for instance, the beginning or the end of a packet.

A summarized description of these packet formats is presented below in order to highlight their structure. For a detailed description of the CoaXPress packet formats, please refer to the CoaXPress standard.

# 5.5.1 Low-speed connection trigger

The packet format for low-speed connection triggers is only used in the low-speed upconnection.

| Char  | Content  | Description                                                 |

|-------|----------|-------------------------------------------------------------|

|       | Either   |                                                             |

| 0 – 2 | K28.2    | Trigger packet indication – LinkTrigger0                    |

|       | K28.4    |                                                             |

|       | K28.4    |                                                             |

|       | or       |                                                             |

|       | K28.4    | Trigger packet indication – LinkTrigger1                    |

|       | K28.2    |                                                             |

|       | K28.2    |                                                             |

| 3 – 5 | 3x Delay | Delay value between the trigger event and its transmission. |

### Table 5 - CoaXPress low-speed connection trigger packet format

Comment: The CoaXPress 2.1 standard also defines an additional low-speed trigger packet format that repurposes the LSB of the delay value to enable two extra triggers, LinkTrigger2 and LinkTrigger3. As this additional packet format has a similar structure and character count as the one presented in Table 5, the CoaXPress over Fiber specification supports both packet formats.

# 5.5.2 High-speed connection trigger

The packet format for high-speed connection triggers consists of three words where each word contains one character replicated four times for redundancy. This packet format starts with a K28.2 character.

| Table 6 - CoaXPress high-speed | d connection trigger packet format |

|--------------------------------|------------------------------------|

|--------------------------------|------------------------------------|

| Word | Content            | Description                                                                                            |

|------|--------------------|--------------------------------------------------------------------------------------------------------|

| 0    | 4x K28.2           | Trigger packet indication                                                                              |

| 1    | 4x Delay           | Delay value between the trigger event and its transmission.                                            |

| 2    | 4x<br>LinkTriggerN | A number N between 0 and 15 which defines the trigger, corresponding to LinkTrigger0 to LinkTrigger15. |

Comment: The current CoaXPress over Fiber specification does not support high-speed trigger packets from CoaXPress 1.x, which are formed by two words instead of three. The support of this packet format from CoaXPress 1.x was not a requirement for CoaXPress over Fiber since no products supporting this feature were registered with JIIA.

### 5.5.3 I/O acknowledgment

The packet format for I/O acknowledgment consists of two words where each word contains one character replicated four times for redundancy. This packet format starts with a K28.6 character.

| Word | Content  | Description                          |  |  |

|------|----------|--------------------------------------|--|--|

| 0    | 4x K28.6 | I/O acknowledgment packet indication |  |  |

| 1    | 4x Code  | 0x01 Trigger packet received OK      |  |  |

Table 7 - CoaXPress I/O acknowledge packet format

### 5.5.4 Data packet transmission

The data packet transmission format is used to exchange data between Device and Host. Typically, this packet format is predominant in terms of bandwidth utilization. It consists of three words where each word contains one character replicated four times for redundancy. Additional *D* words carry the data payload. The packet itself contains two K-code characters to mark start and end of packet (K27.7 and K29.7 respectively). Stream data packets (data packets with Type = 0x01) can also contain one or more K28.3 characters corresponding to stream markers.

| Word        | Content   | Description                                |

|-------------|-----------|--------------------------------------------|

| 0           | 4x K27.7  | Start of packet indication                 |

| 1           | 4х Туре   | Data packet type                           |

| 2           | Data      | Data packet payload of <i>D</i> data words |

| <i>D</i> +1 | (4 bytes) |                                            |

| D+2         | 4x K29.7  | End of packet indication                   |

Table 8 - CoaXPress data packet transmission format

# 5.6 Support of 25G fiber bit rate

The CoaXPress standard defines bit rates up to 12.500 Gbps (CXP-12). These bit rates correspond to the speeds supported by the serial data technology available for coaxial cables that guarantee a reliable link with a cable length going up to 200+ meters. With the introduction of CoaXPress over Fiber, Ethernet

compliant components can be used to go beyond the CoaXPress defined bit rates and cable lengths as in the case of the 25GMII (see section 4.1). To support the 25GMII, CoaXPress over Fiber defines the CXP Speeds *CXP-25 and CXP-31*. A comparison of the high-speed connection bit rates at the transmission media for each supported interface is indicated in the following table:

| CXP<br>Speed | Effective<br>Bit Rate (Gbps) | Coaxial – 8B/10B<br>Bit Rate (Gbps) | 10G Fiber – 64B/66B<br>Bit Rate (Gbps) | 25G Fiber – 64B/66B<br>Bit Rate (Gbps) |

|--------------|------------------------------|-------------------------------------|----------------------------------------|----------------------------------------|

| CXP-1        | 1.000                        | 1.250                               | 10.3125                                | 25.78125                               |

| CXP-2        | 2.000                        | 2.500                               | 10.3125                                | 25.78125                               |

| CXP-3        | 2.500                        | 3.125                               | 10.3125                                | 25.78125                               |

| CXP-5        | 4.000                        | 5.000                               | 10.3125                                | 25.78125                               |

| CXP-6        | 5.000                        | 6.250                               | 10.3125                                | 25.78125                               |

| CXP-10       | 8.000                        | 10.000                              | 10.3125                                | 25.78125                               |

| CXP-12       | 10.000                       | 12.500                              | 10.3125                                | 25.78125                               |

| CXP-25       | 20.000                       | 25.000                              | N/A                                    | 25.78125                               |

| CXP-31       | 25.000                       | 31.250                              | N/A                                    | 25.78125                               |

#### Table 9 – Supported high-speed connection bit rates

Comment: The bit rates for 10G and 25G Fiber are always the nominal for the transmission media and do not change in function of the selected CXP Speed (see section 9).

Comment: CXP-12 has the same effective bit rate of 10 Gbps for Coaxial and 10G Fiber media when we exclude the encoding overhead (8B/10B and 64B/66B respectively).

Comment: CXP-31 has the same effective bit rate of 25 Gbps for Coaxial and 25G Fiber media when we exclude the encoding overhead (8B/10B and 64B/66B respectively).

To select the connection speeds CXP-25 and CXP-31 at the Device via the bootstrap registers *ConnectionConfig* and *ConnectionConfigDefault*, CoaXPress over Fiber defines an extension of the bit rate codes of the *Connection speed* [15:0] field as indicated in the following table:

| CXP Speed | Bit Rate Code |

|-----------|---------------|

| CXP-1     | 0x28          |

| CXP-2     | 0x30          |

| CXP-3     | 0x38          |

| CXP-5     | 0x40          |

| CXP-6     | 0x48          |

| CXP-10    | 0x50          |

| CXP-12    | 0x58          |

| CXP-25    | 0x70          |

| CXP-31    | 0x78          |

#### Table 10 – Bit rate codes

# 6 CXP-PHY bridge specification

The CoaXPress-to-Ethernet Physical Layer bridge (CXP-PHY bridge) specification was designed to guide the development of a CXP-PHY bridge IP. The CXP-PHY bridge IP is intended to be placed between the CoaXPress cores (Device or Host) and the Ethernet PHY IP in order to map the CoaXPress protocol into the nGMII interface.

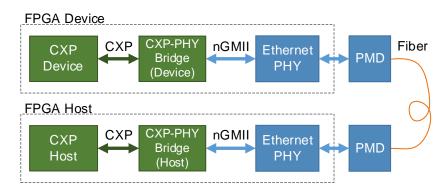

Figure 5 - CoaXPress over Fiber link overview

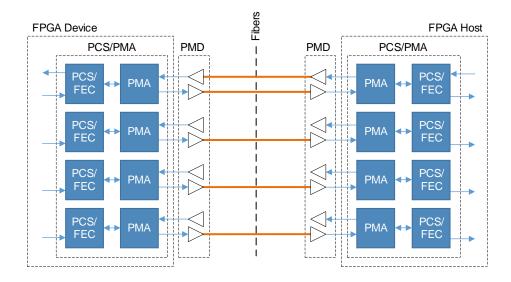

# 6.1 CoF physical layer topology

In terms of physical layer topology, the CXP-PHY bridge targets an asymmetrical configuration where the CoaXPress master connection requires two fibers (one upconnection and one downconnection) and any other extension connection only requires one fiber (downconnection).

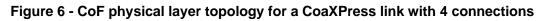

# 6.2 Bridge structure

To support the CoaXPress link specificities, two types of CXP-PHY bridge are specified, one for the Host and the other for the Device. In a CoaXPress multi-connection link, one CXP-PHY bridge is required per connection. Due to the asymmetrical nature of the targeted physical layer topology, the upconnection

mapping section in both bridge types (Host and Device) are only required at the CoaXPress master connections. Other connections only require the downconnection mapping section.

### Figure 7 - CoaXPress over Fiber link via the CXP-PHY Bridge

Comment: It is important to highlight that both Host Logic and Device Logic must be dimensioned to support the maximum throughput of the Ethernet PHY to avoid the overflow of their internal coupler FIFOs.

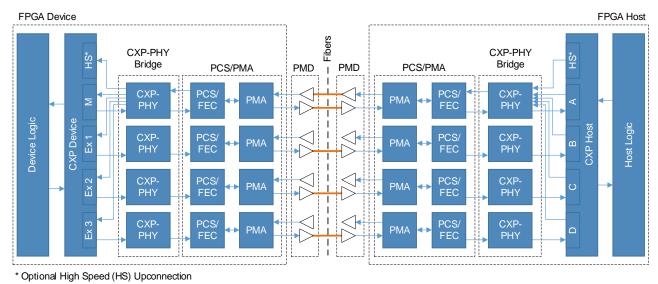

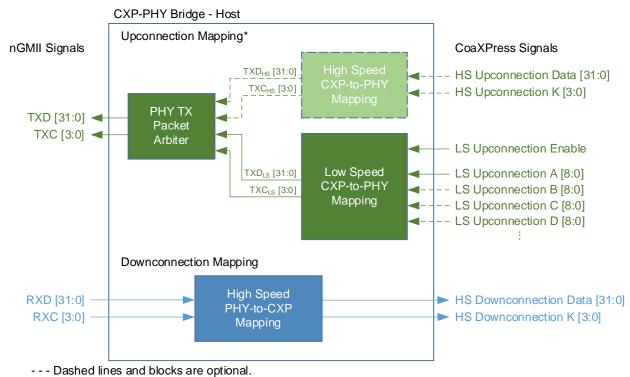

# 6.2.1 CXP-PHY Bridge - Host

\* Only required on CoaXPress Master connections.

### Figure 8 - CXP-PHY Bridge type Host

The CXP-PHY bridge type Host is divided into two parts, one for the CoaXPress downconnection mapping and the other for the CoaXPress upconnection mapping. The downconnection mapping part maps the nGMII RX signals into a CoaXPress high-speed downconnection compliant interface. The upconnection mapping part maps one or more CoaXPress low-speed upconnections and optionally a high-speed upconnection into the nGMII TX signals. The upconnection mapping part is only required on the CXP-PHY bridge connected to a Device master connection.

Comment: Hosts supporting multi-Device topologies must have multi-instances of the upconnection mapping mechanism, one for each CXP-PHY bridge connected to a Device master connection.

At the CoaXPress side, the high-speed upconnection and downconnection ports are composed of four 8bit data signals and their corresponding K-code flags. The low-speed upconnection port is composed of a signal set (one 8-bit data signal and its K-code flag) for each low-speed upconnection. Due to the difference in bandwidth between the CoaXPress low-speed upconnection and the nGMII interface, an additional *Enable* signal is required to indicate when the data is available at this port.

The PHY TX Packet Arbiter maps one of its input signal sets to the nGMII TX signals. The arbitration mechanism is straightforward since CoaXPress does not allow a Host to use high-speed and low-speed upconnections at the same time, i.e., there are no conflicts between high-speed and low-speed packets.

- **Note:** The CoaXPress signal set presented here is only an example to illustrate the CoaXPress interface. To be compatible with existing CoaXPress cores, additional control signals such as a SerDes *bit-clock lock*, may be necessary.

- **Note:** The CoaXPress low-speed upconnection interface may require to deserialize and decode 8B/10B characters to be compatible with existing CoaXPress cores.

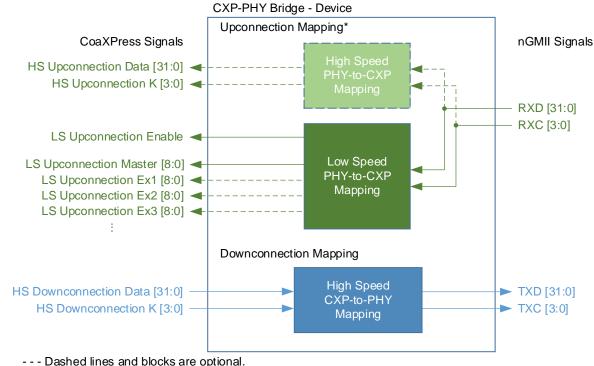

### 6.2.2 CXP-PHY Bridge – Device

\* Only required on CoaXPress Master connections.

#### Figure 9 - CXP-PHY Bridge type Device

The CXP-PHY bridge type Device is divided into two parts, one for the CoaXPress downconnection mapping and the other for the CoaXPress upconnection mapping. The downconnection mapping part maps the CoaXPress high-speed downconnection into a nGMII TX compliant interface. The upconnection mapping part maps the nGMII RX signals into one or more CoaXPress and low-speed upconnections and optionally to a high-speed upconnection. The upconnection mapping part is only required on the CXP-PHY bridge connected to the Device master connection. No arbitration on the nGMII RX signals is required since the low-speed and high-speed PHY-to-CXP mapping modules only process their corresponding packet types.

At the CoaXPress side, the high-speed upconnection and downconnection ports are composed of four 8bit data signals and their corresponding K-code flags. The low-speed upconnection port is composed of a signal set (one 8-bit data signal and its K-code flag) for the master upconnection and one signal set for each existing extension connection. Due to the difference in bandwidth between the CoaXPress low-speed upconnection and the nGMII interface, an additional *Enable* signal is required to indicate when the data is available at this port.

- **Note:** The CoaXPress signal set presented here is only an example to illustrate the CoaXPress interface. To be compatible with existing CoaXPress cores, additional control signals such as a SerDes *bit-clock lock*, may be necessary.

- **Note:** The CoaXPress low-speed upconnection interface may be required to encode the output data to 8B/10B characters and then serialize them to be compatible with existing CoaXPress cores.

# 6.3 Packet structure

The words that constitute the CXP-PHY packet stream are briefly described in the following table:

| Word Type                    | Notation | Size<br>(characters) | Description                                                                                             |

|------------------------------|----------|----------------------|---------------------------------------------------------------------------------------------------------|

| Start of Packet              | SOP      | 4                    | Marks the start of a CXP-PHY packet                                                                     |

| End of Packet                | EOP      | 8                    | Marks the end of a CXP-PHY packet                                                                       |

| Idle Transfer                | IT       | 4                    | Interpacket gap (IPG)                                                                                   |

| High-speed Data<br>Payload   | HDP      | 4                    | High-speed payload word containing 4 bytes of data                                                      |

| High-speed K-code<br>Payload | НКР      | 4                    | High-speed payload word containing 4 K-code characters                                                  |

| Low-speed Payload            | LSP      | 4                    | Low-speed payload word containing 2 bytes of<br>control and 2 bytes of data and/or K-code<br>characters |

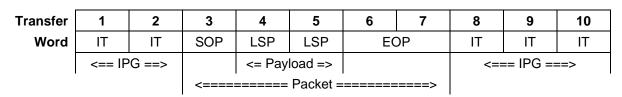

All CXP-PHY packets are formed as SOP + *Payload* + EOP.

All CXP-PHY packets shall contain at least one Payload word (HDP, HKP, or LSP).

The CXP-PHY bridge uses two types of packets in nGMII stream: high-speed and low-speed packets.

High-speed packets are used to transmit data from a *High-Speed CXP-to-PHY Mapping* module to a *High-Speed PHY-to-CXP Mapping* module. The payload of CXP-PHY high-speed packets is formed by one HKP and/or one or more HDP words. An HKP word is always preceded by a SOP and followed by an HDP or an EOP.

Low-speed packets are used to transmit data from a *Low-Speed CXP-to-PHY Mapping* module to a *Low-Speed PHY-to-CXP Mapping* module. The payload of CXP-PHY low-speed packets is formed by one or more LSP words.

| Transfer                               | 1      | 2      | 3                 | 4   | 5   | 6     | 7  | 8  | 9      | 10    |

|----------------------------------------|--------|--------|-------------------|-----|-----|-------|----|----|--------|-------|

| Word                                   | IT     | IT     | SOP               | HKP | HDP | HDP   | EC | )P | IT     | IT    |

|                                        | <== IP | 'G ==> | <===== Payload == |     |     | ====> |    |    | <== IP | G ==> |

| <===================================== |        |        |                   |     |     |       |    |    |        |       |

Figure 10 - Example of a CXP-PHY high-speed packet

### Figure 11 - Example of a CXP-PHY low-speed packet

A description of all valid words in a CXP-PHY packet is listed below.

Note: In a CXP-PHY packet, all reserved or not in use fields in a word shall be set to "0".

## 6.3.1 SOP – Start of Packet

The SOP word marks the start of a CXP-PHY packet at the nGMII interface for both up and down connections.

| Word | Lane | TXC/RXC | TXD/RXD        |

|------|------|---------|----------------|

| 0    | 0    | 1       | [7:0] Start    |

|      | 1    | 0       | [7:0] SopCtrl  |

|      | 2    | 0       | [7:0] SopData0 |

|      | 3    | 0       | [7:0] SopData1 |

Table 12 – Start of Packet (SOP) word format

The SOP fields are described below.

### 6.3.1.1 Start

Start[7:0] - Start control character respecting nGMII Rule #1.

0xFB => nGMII control character /S/

#### 6.3.1.2 SopCtrl

#### SopCtrl[7] - Packet type

When "0" => Low-speed packet (see section 8 Low-speed mapping for details)

When "1" => High-speed packet (see section 7 High-speed mapping for details)

#### SopCtrl[6:4] - Reserved

**SopCtrl[3:0]** - Control field dependent on the packet type (SopCtrl[7])

For low-speed packets (SopCtrl[7] = "0"), the Control field informs the upconnection status:

#### SopCtrl[3] - Update flag

```

When "0" => No update

```

When "1" => Upconnection status (SopCtrl[1:0]) updated

#### SopCtrl[2] - Reserved

SopCtrl[1] - Low-speed rate

```

When "0" => 20.83' Mbps<sup>1</sup>

```

When "1" => 41.6' Mbps<sup>2</sup>

SopCtrl[0] - High-speed upconnection state

When "0" => Deactivated

When "1" => Activated

This control field is used in the upconnection mapping mechanism to inform the CXP-PHY Bridge in the Device about the upconnection status in the Host side (see section 9). The bits SopCtrl[0] and SopCtrl[1]

<sup>&</sup>lt;sup>1</sup> The dot after the number 3 means "3 recurring", i.e. the bitrate is 20.833333... Mbps.

<sup>&</sup>lt;sup>2</sup> The dot after the number 6 means "6 recurring", i.e. the bitrate is 41.666666... Mbps.

must report the upconnection status in every low-speed packet. The bit SopCtrl[3] is set to "1" only in packets where the Upconnection status is different from the previous one, otherwise this bit shall be set to "0".

For high-speed packets (SopCtrI[7] = "1"), the Control field informs the next word type in the stream:

SopCtrl[3:1] - Reserved

SopCtrl[0] - Next word type

When "0" => HDP When "1" => HKP

### 6.3.1.3 SopData0

SopData0[7:0] - Embedded K-code (replaces a CoaXPress K-code replicated four times)

When "0x00" => No embedded K-code When "0x5C" => K28.2 - High-speed trigger When "0xDC" => K28.6 - I/O acknowledgment When "0xFB" => K27.7 - Start of data packet indication When others => Reserved

When a K28.2 (high-speed trigger) is embedded into the SopData0, the SopData1 replaces the *Delay* word of the CoaXPress high-speed trigger packet and the *LinkTriggerN* word is mapped in the HDP word that follows the SOP word.

When a K28.6 (I/O acknowledgment) is embedded into the SopData0, the SopData1 is reserved and the *Code* word of the CoaXPress I/O acknowledgment packet is mapped in the HDP word that follows the SOP word.

When a K27.7 (start of data packet indication) is embedded into the SopData0, the SopData1 replaces the *Type* word of the CoaXPress data packet.

**Note:** The SopData0 field is only valid on high-speed packets (SopCtrl[7] = "1"). On low-speed packets, the SopData0 field is reserved.

### 6.3.1.4 SopData1

SopData1[7:0] - Embedded Data (replaces a CoaXPress byte replicated four times)

The SopData1 field is used when SopData0 is "0x5C" (K28.2 – High-speed trigger) to replace the *Delay* word of the CoaXPress high-speed trigger packet. When the SopData0 is "0xFB" (K27.7 – Start of data packet indication), the SopData1 field replaces the *Type* word of the CoaXPress data packet. For all other cases, the SopData1 field is reserved.

**Note:** The SopData1 field is only valid on high-speed packets (SopCtrl[7] = "1"). On low-speed packets, the SopData1 field is reserved.

## 6.3.2 EOP – End of Packet

The EOP word marks the end of a CXP-PHY packet at the nGMII interface for both up and down connections.

| Word | Lane | TXC/RXC | TXD/RXD          |

|------|------|---------|------------------|

| 0    | 0    | 0       | [7:0] EopData0   |

|      | 1    | 0       | [7:0] EopData1   |

|      | 2    | 1       | [7:0] Terminate  |

|      | 3    | 1       | [7:0] nGMII IDLE |

| 1    | 0    | 1       | [7:0] nGMII IDLE |

|      | 1    | 1       | [7:0] nGMII IDLE |

|      | 2    | 1       | [7:0] nGMII IDLE |

|      | 3    | 1       | [7:0] nGMII IDLE |

Table 13 - End of Packet (EOP) word format

The EOP fields are described below.

#### 6.3.2.1 EopData0

EopData0[7:0] - Embedded K-code (replaces a CoaXPress K-code replicated four times)

When "0x00" => No embedded K-code

When "0x7C" => K28.3 - Stream marker

When "0xFD" => K29.7 - End of data packet indication

When others => Reserved

When the EopData0 has no embedded K-code, it indicates that the EOP was originated by 8B/10B IDLEs or high-priority packets embedded into the CoaXPress stream (see sections 7.1.2 and 7.1.3).

When a K28.3 is embedded into the EopData0, it indicates that the EOP was originated in order to introduce a CoaXPress stream marker into the nGMII stream (see section 7.1.2).

When a K29.7 is embedded into the EopData0, it indicates that the EOP was originated by a CoaXPress end of data packet (see section 7.1.2).

**Note:** The EopData0 field is only valid on high-speed packets (SopCtrl[7] = "1"). On low-speed packets, the EopData0 field is reserved.

### 6.3.2.2 EopData1

EopData1[7:0] - Reserved

### 6.3.2.3 Terminate

Terminate[7:0] - Terminate control character

0xFD => nGMII control character /T/

#### 6.3.2.4 nGMII IDLE

**nGMII IDLE[7:0]** - Idle control character

0x07 => nGMII IDLE control character /I/

Note: The EOP contains 5 nGMII IDLE characters respecting nGMII Rules #2 and #3.

### 6.3.3 IT – Idle Transfer

IT words form the IPG and are used when there are no packets to be transferred in the nGMII data stream. IT words are formed by four nGMII IDLE control characters /l/ (0x07).

Table 14 - Idle Transfer (IT) word format

| Word | Lane | TXC/RXC | TXD/RXD          |

|------|------|---------|------------------|

| 0    | 0    | 1       | [7:0] nGMII IDLE |

|      | 1    | 1       | [7:0] nGMII IDLE |

|      | 2    | 1       | [7:0] nGMII IDLE |

|      | 3    | 1       | [7:0] nGMII IDLE |

### 6.3.4 HDP – High-Speed Data Payload

Word containing 4 bytes of data payload.

#### Table 15 - High-Speed Data Payload (HDP) word format

| Word | Lane | TXC/RXC | TXD/RXD                  |

|------|------|---------|--------------------------|

| 0    | 0    | 0       | [7:0] Data stream Byte 0 |

|      | 1    | 0       | [7:0] Data stream Byte 1 |

|      | 2    | 0       | [7:0] Data stream Byte 2 |

|      | 3    | 0       | [7:0] Data stream Byte 3 |

### 6.3.5 HKP – High-Speed K-Code Payload

Word containing four K-code characters of payload.

#### Table 16 - High-Speed K-Code Payload word format

| Word | Lane | TXC/RXC | TXD/RXD                    |

|------|------|---------|----------------------------|

| 0    | 0    | 0       | [7:0] Data stream K-code 0 |

|      | 1    | 0       | [7:0] Data stream K-code 1 |

|      | 2    | 0       | [7:0] Data stream K-code 2 |

|      | 3    | 0       | [7:0] Data stream K-code 3 |

**Note:** The HKP word includes only the K-code corresponding hexadecimal value without the K-code bit flag.

### 6.3.6 LSP – Low-Speed Payload

LSP words form the payload of nGMII low-speed packets.

| Table 17 - Low-Speed F | Payload (LSP) | word format |

|------------------------|---------------|-------------|

|------------------------|---------------|-------------|

| Word | Lane | TXC/RXC | TXD/RXD            |  |  |

|------|------|---------|--------------------|--|--|

| 0    | 0    | 0       | [7:0] LspCtrlSlot0 |  |  |

|      | 1    | 0       | [7:0] LspCharSlot0 |  |  |

|      | 2    | 0       | [7:0] LspCtrlSlot1 |  |  |

|      | 3    | 0       | [7:0] LspCharSlot1 |  |  |

The LSP fields are described below.

#### 6.3.6.1 LspCtrlSlotn

LspCtrlSlotn[7:2] - Reserved

LspCtrlSlotn[1:0] - Indicates the character type at the Character Slot n field

When "00" => Not in use

When "01" => Data

When "10" => K-code

When "11" => Reserved

#### 6.3.6.2 LspCharSlotn

Character from a corresponding CoaXPress low-speed connection.

# 7 High-speed CXP-PHY mapping

The high-speed CXP-PHY mapping mechanism covers CoaXPress high-speed connections (up and down) mapping to/from a nGMII interface. This section describes the mapping procedure for each element present in the CoaXPress data stream. This section also presents an analysis of the bandwidth overhead introduced by the CXP-PHY mapping mechanism.

# 7.1 CXP-to-PHY mapping

**Note:** All examples in this section do not consider the relative latencies between the *CXP Stream* and the *nGMII Stream*. For detailed examples, please refer to Annex A.

## 7.1.1 CoaXPress 8B/10B IDLE words

All 8B/10B IDLE words are removed from the CoaXPress stream at the CXP-to-PHY mapping. This saves at least 1% of the bandwidth in the nGMII since a minimum of one 8B/10B IDLE word must be inserted into the CoaXPress data stream every 100 words. Removing 8B/10B IDLE words also simplifies the mapping since they differ from regular CoaXPress K-code words, which include one K-code replicated four times. When there is no data to be transferred, IT words are introduced into the IPG to fill the nGMII stream.

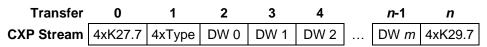

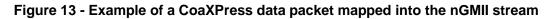

## 7.1.2 CoaXPress data packets

CoaXPress data packets are formed as follows:

Figure 12 - Example of a CoaXPress data packet

The procedure to map data packets into the nGMII stream is to replace the 4xK27.7 and 4xType words by an SOP word and to replace the 4xK29.7 word by an EOP word. The CoaXPress Data Words (DWs) are simply mapped into HDP words.

As a result, we obtain:

| Transfer     | 0    | 1    | 2    | 3    |  | <i>n</i> -2 | <i>n</i> -1 | n       |

|--------------|------|------|------|------|--|-------------|-------------|---------|

| nGMII Stream | SOP  | HDP  | HDP  | HDP  |  | HDP         | EC          | )P      |

| Lane 0       | /S/  |      |      |      |  |             | 0xFD        |         |

| Lane 1       | 0x80 |      | DW 1 |      |  | DW m        | 0x00        | Av. /1/ |

| Lane 2       | 0xFB | DW 0 |      | DW 2 |  |             | /T/         | 4x /l/  |

| Lane 3       | Туре |      |      |      |  |             | /I/         |         |

CoaXPress data packets can also include one or more stream marker words that contain a K28.3 character replicated four times and 8B/10B IDLE words for packet stretching.

A data buffer is required in the CXP-to-PHY mapping module to guarantee that nGMII packets are continuous. If this buffer becomes empty, the packet must be terminated since nGMII IDLE characters are not allowed within a nGMII packet. In case 8B/10B IDLE words are embedded in a CoaXPress data packet, the packet may have to be split into two nGMII packets to introduce IT words until more data is available for transmission. The following example illustrates this case considering that the internal buffer at the CXPto-PHY mapping module becomes empty:

nGMII Stream Lane 0 Lane 1 Lane 2

| Stream | HDP   | HDP   | EC   | OP     | IT     | SOP  | HDP   | HDP   |   |

|--------|-------|-------|------|--------|--------|------|-------|-------|---|

| Lane 0 |       |       | 0x00 |        |        | /S/  |       |       |   |

| Lane 1 | DW 40 |       | 0x00 | A /1/  | A /1/  | 0x80 |       |       |   |

| Lane 2 | DW 10 | DW 11 | /T/  | 4x /l/ | 4x /l/ | 0x00 | DW 12 | DW 13 |   |

| Lane 3 |       |       | /I/  |        |        | 0x00 |       |       |   |

|        |       |       |      |        |        |      |       |       | • |

### Figure 14 - Mapping a CoaXPress data packet with embedded 8B/10B IDLE words

When one or more stream marker words (4xK28.3) are embedded in a CoaXPress data packet, the marker is replaced by an EOP followed by a SOP to resume packet transmission.

**CXP Stream** ... DW 10 DW 11 DW 12 4xK28.3 DW 13 DW 14

|              |       |       |               |      |          |      |       |       | _ |

|--------------|-------|-------|---------------|------|----------|------|-------|-------|---|

| nGMII Stream | HDP   | HDP   | HDP           | EOP  |          | SOP  | HDP   | HDP   |   |

| Lane 0       |       |       |               | 0x7C |          | /S/  |       |       |   |

| Lane 1       | DW 40 |       | <b>D</b> W 40 | 0x00 | 4 yr /1/ | 0x80 | DW 13 | DW 14 |   |

| Lane 2       | DW 10 | DW 11 | DW 12         | /T/  | 4x /l/   | 0x00 |       |       |   |

| Lane 3       |       |       |               | /١/  |          | 0x00 |       |       |   |

### Figure 15 - Mapping a CoaXPress data packet with embedded stream marker words

When splitting a CoaXPress packet into two or more nGMII packets, it is mandatory that the resulting packets have at least one word of payload.

#### 7.1.3 **High-priority packets**

High-priority CoaXPress packets are specific packets that can be formed by two words (I/O acknowledgement) or three words (high-speed trigger). They do not present regular start and end of packet markers (K27.7 and K29.7 respectively). The high-speed CXP-PHY mapping mechanism shall map highpriority packets into the nGMII stream as soon as they are detected in the CoaXPress stream, thus bypassing any data buffer in the CXP-to-nGMII mapping module.

Three cases must be taken into consideration during mapping:

- Isolated high-priority packets •

- High-priority packets embedded in data packets

- High-speed trigger packet embedded in a I/O acknowledgement packet

Lane 2

Lane 3

Isolated high-priority packets are present in the CoaXPress data stream outside of a data packet. In this case, there is no packet in the nGMII stream to be terminated. The following example illustrates this case:

| CXP Stream   | IDLE   | IDLE    | 4xK28.2 | 4xDelay | 4xTrgN       | IDLE    | IDLE    |   |

|--------------|--------|---------|---------|---------|--------------|---------|---------|---|

|              |        |         |         |         |              |         |         | _ |

| nGMII Stream | IT     | IT      | SOP     | HDP     | EC           | P       | IT      |   |

| Lane 0       |        |         | /S/     |         | 0x00         |         |         |   |

| Lane 1       | 4.4.11 | 457 /1/ | 0x80    | 4       | 0x00         | 4.4.11/ | 4.7 /1/ |   |

| 1            | 4x /l/ | 4x /l/  | 0.50    | 4xTrgN  | / <b>T</b> / | 4x /l/  | 4x /l/  |   |

0x5C

Delay

/T/

/I/

| Figure 16 - | Mapping an | isolated | high-priority  | packet |

|-------------|------------|----------|----------------|--------|

| i iguio i o | mapping an | loolatoa | ingin priority | paonot |

When a high-priority packet is embedded in a data packet, the corresponding nGMII packet must be terminated before inserting the high-priority packet. Once the high-priority packet data is inserted into the new nGMII packet, the latter needs to be terminated only if the following word in the CoaXPress stream is a K-code or no other word is available for transmission. The following examples illustrate the high-priority packets mapping procedure:

| CXP Stream | DW 10 | DW 11 | 4xK28.6 | 4xCode | DW 12 | DW 13 | . |

|------------|-------|-------|---------|--------|-------|-------|---|

|------------|-------|-------|---------|--------|-------|-------|---|

| nGMII Stream | HDP   | HDP   | EOP  |        | SOP  | HDP    | HDP   | HDP   | ]     |

|--------------|-------|-------|------|--------|------|--------|-------|-------|-------|

| Lane 0       | DW 10 | DW 11 | 0x00 |        | /S/  |        |       |       |       |

| Lane 1       |       |       | 0x00 | 4x /l/ | 0x80 | 4vCada |       | DW 13 |       |

| Lane 2       |       |       | /T/  |        | 0xDC | 4xCode | DW 12 |       | DW 15 |

| Lane 3       |       |       | /I/  |        | 0x00 |        |       |       |       |

#### Figure 17 - Mapping a CoaXPress data packet with embedded I/O acknowledge packet

**Note:** The 4xCode word is not embedded in the SOP because, as stated before, a nGMII packet must be formed by at least one word of payload.

| CXP Stream   | . DW 10 | DW 11 | 4xK28.2 | 4xDelay | 4xTrgN | DW 12  | DW 13 | ]     |   |

|--------------|---------|-------|---------|---------|--------|--------|-------|-------|---|

| nGMII Stream | . HDP   | HDP   | EC      | סר      | SOP    | HDP    | HDP   | HDP   | 1 |

|              |         | пре   | EC      | 76      | 305    | пре    | пре   | пре   |   |

| Lane 0       |         |       | 0x00    |         | /S/    |        |       |       |   |

| Lane 1       | DW 10   | DW 11 | 0x00    | 4x /l/  | 0x80   | 4xTrgN | DW 12 | DW 13 |   |

| Lane 2       |         | DWII  | /T/     | 47 /1/  | 0x5C   |        |       | DW 13 |   |

| Lane 3       |         |       | /1/     |         | Delay  |        |       |       |   |

Figure 18 - Mapping a CoaXPress data packet with embedded high-speed trigger packet

#### Japan Industrial Imaging Association Guideline

In the case where a high-speed trigger packet is embedded into an I/O acknowledge packet, the highspeed trigger has priority over the I/O acknowledge and must be mapped into the nGMII stream as soon as possible. The following example illustrates this case:

Figure 19 - Mapping a high-speed trigger embedded in an I/O acknowledge packet

To avoid introducing jitter on high-speed trigger packets, it is mandatory to have a fixed latency between the start of a high-speed trigger at the CXP stream (4x K28.2) and its mapped version at the nGMII stream (SOP). Once the start of a high-speed trigger packet is detected in the CXP stream, the mapping mechanism shall wait three transfer cycles before introducing its corresponding SOP. These three cycles are used by the mapping mechanism to properly end a packet that is being transferred in the nGMII stream while respecting the packet structure described in section 6.3. In the case where there is no other packet being transferred while the start of a high-speed trigger packet is detected in the CXP stream, these three cycles shall be filled with IT words.

For more detailed examples of CXP-to-nGMII mapping, please refer to Annex A.

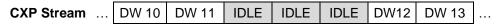

# 7.1.4 Use of HKP words

HKP words are used to map K-code words into the nGMII stream when these words cannot be embedded into an SOP or an EOP. One example of this situation is when there is no CXP-PHY packet being transferred and the only data available in the data buffer is a K-code word. In this case, an HKP word is used in order to respect the minimum payload size of one word.

| CXP Stream   | DW10 | IDLE | IDLE    | IDLE    | 4xK29.7 | IDLE |      |         |        |   |

|--------------|------|------|---------|---------|---------|------|------|---------|--------|---|

|              |      |      |         |         |         |      |      |         |        | _ |

| nGMII Stream | HDP  | EC   | OP      | IT      | SOP     | HKP  | EC   | )P      | IT     |   |

| Lane 0       |      | 0x00 |         |         | /S/     | 0xFD | 0x00 |         |        |   |

| Lane 1       | DW10 | 0x00 | 4x /l/  | 4x /l/  | 0x81    | 0xFD | 0x00 | 4x /l/  | 4x /l/ |   |

| Lane 2       | DWIU | /T/  | 4X / 1/ | 4X / 1/ | 0x00    | 0xFD | /T/  | 4X / 1/ | 4X /I/ |   |

| Lane 3       |      | /I/  |         |         | 0x00    | 0xFD | /I/  |         |        |   |

**Note:** An HKP word is always preceded by a SOP and followed by an HDP or an EOP (see section 6.3).

# 7.2 PHY-to-CXP mapping

The PHY-to-CXP mapping mechanism is responsible for the reconstruction of the CoaXPress data stream based on nGMII packets generated by the CXP-to-PHY mapping module. A data buffer is required in this module to be able to halt the input stream when decoding a SOP word, inserting 8B/10B IDLE words or a high-priority message into the CoaXPress data stream.

8B/10B IDLE words are reinserted into the data stream at a minimum rate of one 8B/10B IDLE word every 100 words and whenever no data is available at the receiver. As the 8B/10B IDLE words are not present in the nGMII stream, the PHY-to-CXP mapping module freely determines the position where they are reinserted in the CoaXPress data stream. The only restriction is that 8B/10B IDLE words cannot be inserted into a high-priority packet as stated in the CoaXPress standard.

# 7.3 Overhead analysis

The CoaXPress bandwidth usage is dominated by data packet transfers. The bandwidth necessary to transfer high-priority packets and mandatory 8B/10B IDLE words is virtually negligible (~1%). The CXP-to-PHY mapping mechanism basically does not introduce overhead when mapping data packets into nGMII packets. However, for any K-code embedded in a CoaXPress data packet (i.e., stream markers and high-priority packets), the mapping mechanism must terminate the current nGMII packet to announce the new K-code in a SOP word. This process introduces two words of overhead.

The ratio of embedded K-code characters in comparison with regular data words is strongly dependent on the size of lines being transferred from Device to Host. The following examples illustrate that.

### 7.3.1 Example 1 – Area Scan

The CoaXPress data stream parameters for this example are:

Pixel format = Mono8

Number of embedded I/O ack. = 2 per frame

Number of CXP connections = 1

| Table 18 - nGMII mappin | g overhead for area sc | an applications |